# CMS32C030 Datasheet

32-bit microcontrollers based on ARM® Cortex®-M0+

64KB Flash, analog functions, Timers, and communication interfaces.

V0.9.1

Please note the following CMS IP policy

<sup>\*</sup> China Micro Semicon Co., Ltd. (hereinafter referred to as the Company) has applied for patents and holds absolute legal rights and interests. The patent rights associated with the Company's MCUs or other products have not been authorized for use, and any company, organization, or individual who infringes the Company's patent rights through improper means will be subject to all possible legal actions taken by the Company to curb the infringement and to recover any damages suffered by the Company as a result of the infringement or any illegal benefits obtained by the infringer.

<sup>\*</sup> The name and logo of Cmsemicon are registered trademarks of the Company.

<sup>\*</sup>The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not authorized for use as critical components in lifesaving, life-sustaining devices or systems. The Company reserves the right to modify the products without prior notice. For the latest information, please visit the official website at www.mcu.com.cn.

#### **Features**

#### **♦** Operation Environment

- Supply voltage range: 2.0V to 5.5V

- Temperature range: -40°C to 85°C

- Low power consumption modes: sleep mode, deep sleep mode

#### **♦** Core

- ARM® 32-bit Cortex®-M0+ CPU

- Operation frequency: 48MHz

#### **♦** 32-Bit Hardware Multiplier

Supports single-cycle 32-bit multiplication operations.

#### **♦** Memory

- 64KB flash memory with shared program and data storage

- 1KB dedicated data flash memory

- 8KB SRAM memory

#### **♦** Power and Reset Management

- Power-on Reset (POR)

- Low voltage detection (LVD) (threshold voltage can be set)

#### **♦** Clock Management

- Internal high-speed oscillator: 48MHz

- Internal low-speed oscillator: 32KHz

- XT1 external crystal oscillator: 32.768KHz

#### **♦** Enhanced DMA

- 3 channels

- Interrupt trigger start

- Supports normal mode, repeat mode and chain transfer

#### **♦** General-Purpose CRC

#### **♦** GPIO

- Up to 30 GPIOs, supports external interrupts

- All GPIOs support pull-up/pull-down resistor functionality

- Some GPIOs can be configured for TTL input or Schmitt input

#### **♦** High Precision 12-Bit ADC

- Conversion rate: 500 Ksps

- Up to 30 external analog channels

- Supports single, continuous, scan, and select modes

- Supports hardware trigger

- Conversion range: 0 to positive reference voltage

## **♦** Analog Comparators (ACMP0/1)

- Multiple selectable positive and negative terminals

- Supports hysteresis voltage selection: 0mV/20mV

- Comparator output can be used as a trigger signal for Timer 1

#### **♦** Rich Timer Resources

- 1x 16-bit advanced control timer (TIM1)

- 4x 16-bit general-purpose timers (TIM3/TIM14/TIM16/TIM17)

- 1x windowed watch dog timer (WWDG)

- 1x independent watch dog timer (IWDG)

- 1x 15-bit interval timer

- SysTick timer

#### Rich and Flexible Interfaces

- 2-channel general-purpose serial communication unit: Supports 3-wire serial (SSPI), UART, simplified I<sup>2</sup>C functions, supports up to 1 UART

- 1x SPI communication unit: Supports 8-bit and 16-bit transfer frames

- 1x I<sup>2</sup>C interface: Supports standard mode (100 KHz) and fast mode (400 KHz)

- 1x serial synchronous/asynchronous communication unit (USART): Supports singlewire half-duplex communication

#### ♦ Safety Features

- Compliant with IEC60730 standards

- Supports hardware CRC

- Supports protection of important SFRs to prevent misoperations

- 128-bit unique ID

- ♦ Serial Two-Wire Debugger (SWD)

# 1 Overview

## 1.1 Brief Introduction

The CMS32C030 uses a high-performance ARM® Cortex®-M0+ 32-bit RISC core, capable of operating at up to 48 MHz. It features high-speed embedded flash memory (8K SRAM, with a maximum of 64KB program/data flash). This product integrates multiple standard interfaces, including I<sup>2</sup>C, UART, and SPI. It also includes several timer modules such as advanced timers and general-purpose timers. The system features a 12-bit A/D converter, enabling the acquisition of external sensor signals, which reduces system design costs.

The CMS32C030 also offers excellent low-power performance, supporting both sleep and deep sleep modes, and provides flexible design options.

www.mcu.com.cn 3 / 60 Rev.0.9.1

# 1.2 Product Model List

## Product list of CMS32C030:

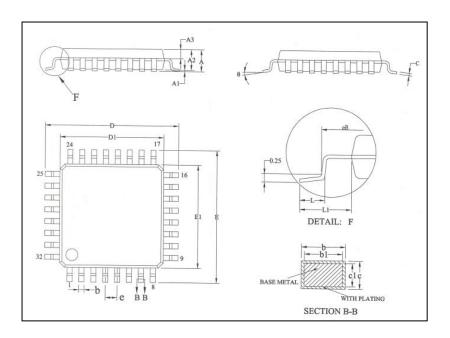

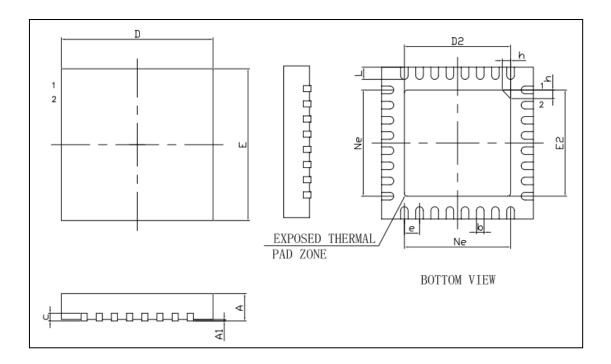

| Product model   | Package                                    | Flash memory | Dedicated data<br>Flash memory | SRAM |

|-----------------|--------------------------------------------|--------------|--------------------------------|------|

| CMS32C030DE32FP | 32-pin plastic LQFP32 (7x7mm, 0.8mm pitch) |              |                                |      |

| CMS32C030DE32NA | 32-pin plastic QFN32 (5x5mm, 0.5mm pitch)  | 64KB         | 1KB                            | 8KB  |

| CMS32C030DE32NB | 32-pin plastic QFN32 (4x4mm, 0.4mm pitch)  |              |                                |      |

www.mcu.com.cn 4 / 60 Rev.0.9.1

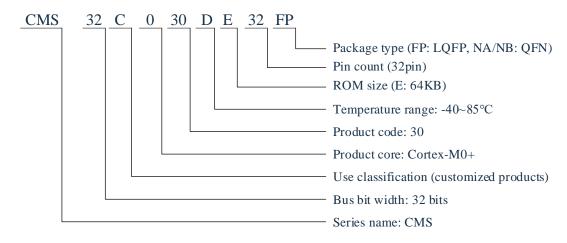

# 1.3 Product Information

Here is the product information for the CMS32C030 chip:

| Product model Peripheral interface |                               |                             | CMS32C030DE32FP                        | CMS32C030DE32NA<br>CMS32C030DE32NB |  |

|------------------------------------|-------------------------------|-----------------------------|----------------------------------------|------------------------------------|--|

| MCU operating voltage              |                               |                             | 2.0V~5.5V                              |                                    |  |

| Maximum                            | clock frequen                 | су                          | 48M                                    | IHz                                |  |

|                                    | ROM                           |                             | 64K 64K                                |                                    |  |

| Memory module                      | Data                          | Flash                       | 1K                                     | 1K                                 |  |

|                                    | SR                            | AM                          | 8K                                     | 8K                                 |  |

|                                    | Sys                           | Tick                        | 1                                      |                                    |  |

|                                    | WV                            | VDG                         | 1                                      |                                    |  |

| T:                                 | IW                            | DG                          | 1                                      |                                    |  |

| Timer                              | 16-bit adv                    | anced timer                 | 1                                      |                                    |  |

|                                    | 16-bit univ                   | versal timer                | 4                                      |                                    |  |

|                                    | 15-bit into                   | erval timer                 | 1                                      | 1                                  |  |

| Enhanced digital                   | C                             | RC                          | 1                                      |                                    |  |

| peripheral                         | DMA (3                        | channels)                   | 1                                      |                                    |  |

|                                    |                               | SSPI                        | 1                                      |                                    |  |

|                                    | SAU                           | UART                        | 1                                      |                                    |  |

| Communication                      |                               | Simplified I <sup>2</sup> C | 1                                      |                                    |  |

| module                             | SPI                           |                             | 1                                      |                                    |  |

|                                    | USART                         |                             | 1                                      |                                    |  |

|                                    | I <sup>2</sup> C              |                             | 1                                      |                                    |  |

|                                    | 12-bi                         | t ADC                       |                                        |                                    |  |

| Analog module                      | (Number of external channels) |                             | 28                                     | 30                                 |  |

|                                    |                               | CMP                         | 2                                      |                                    |  |

| GPIOS                              |                               |                             | 28                                     | 30                                 |  |

| LVD                                |                               |                             | 4.0V/3.65V/3.1V/2.95V/2.85V/2.75V<br>V |                                    |  |

| Operating voltage                  |                               |                             | 2.0V~                                  | 5.5V                               |  |

| Operating temperature              |                               |                             | -40°C to 85°C                          |                                    |  |

| Pa                                 | ackage                        |                             | LQFP32                                 | QFN32                              |  |

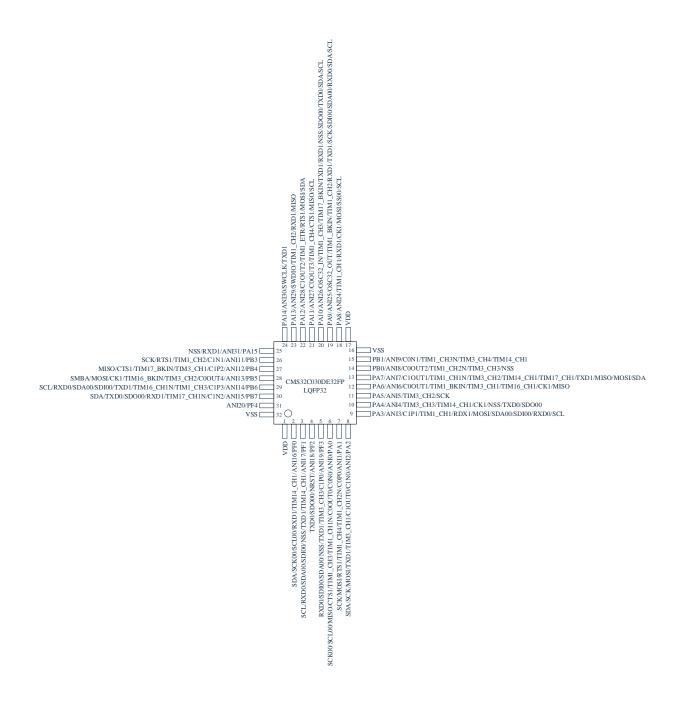

# 1.4 Top View

## 1.4.1 CMS32C030DE32FP

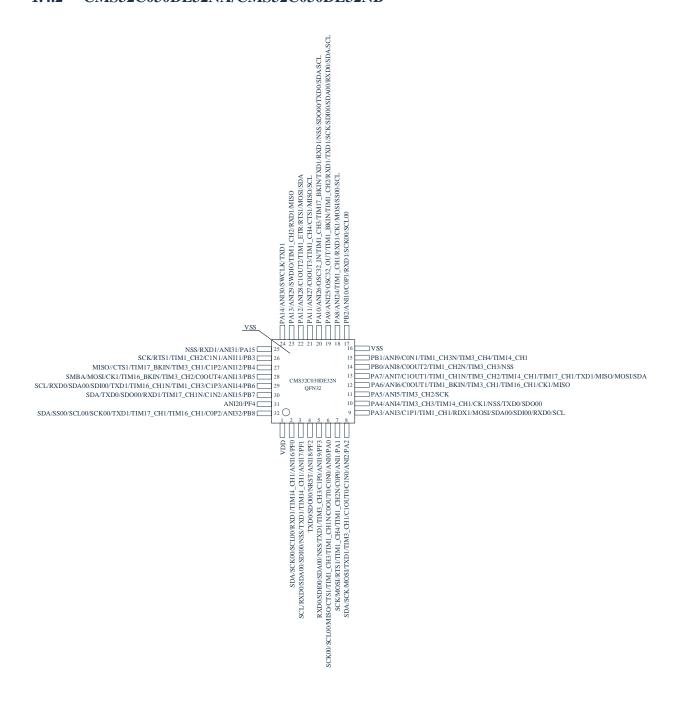

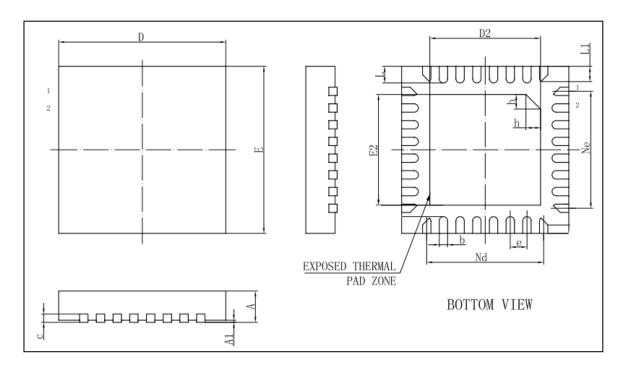

## 1.4.2 CMS32C030DE32NA/CMS32C030DE32NB

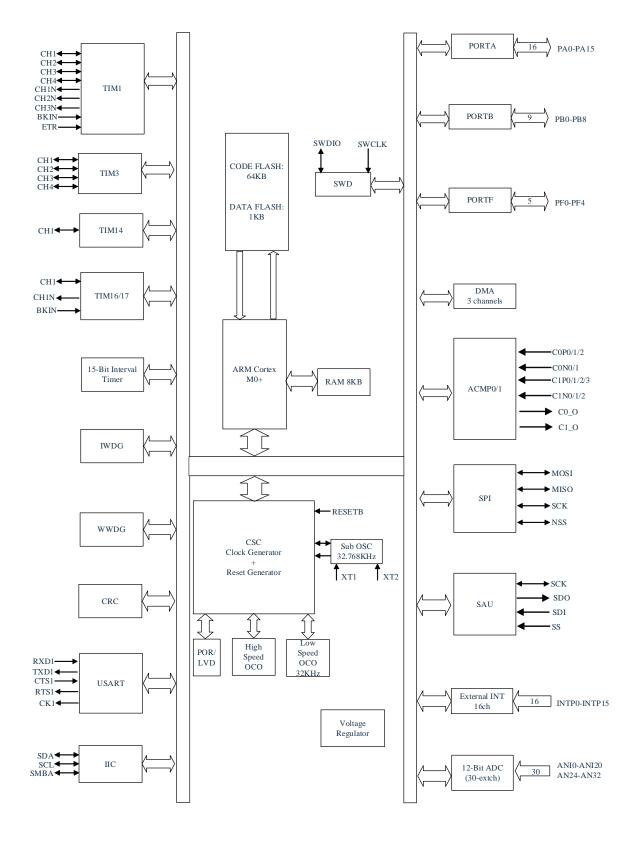

# 2 Product Block Diagram

#### 2.1.1 CMS32C030DE32NA

# 3 Memory Map

| FFFF_FFFFH |                                               |

|------------|-----------------------------------------------|

|            | Reserved                                      |

|            | Reserved                                      |

| E00F_FFFFH | Cortex-M0+ Dedicated Peripheral Resource Zone |

| Е000_0000Н | Conca-wo+ Dedicated Tempheran Resource Zone   |

|            | Reserved                                      |

| 4008_FFFFH |                                               |

|            | Peripheral Resource Zone                      |

|            | T STIPHOLE RESOURCE ZONG                      |

| 4000_0000H |                                               |

|            | Reserved                                      |

| 2000_1FFFH |                                               |

|            | SRAM (8KB)                                    |

| 2000_0000H |                                               |

|            |                                               |

|            | Reserved                                      |

| 0050_05FFH |                                               |

|            | Data Flash 1KB                                |

| 0050_0200H |                                               |

|            | Reserved                                      |

| 0000_FFFFH |                                               |

|            | Main Flash Memory Zone (up to 64KB)           |

|            |                                               |

| 0000_0000H |                                               |

# 4 Pin Functions

# **4.1 Port Functions**

The symbols in the following table are explained as follows:

|          | 8                    |  |

|----------|----------------------|--|

| Pin type | Symbol description   |  |

| I/O      | Digital input/output |  |

| I        | Digital input        |  |

| 0        | Digital output       |  |

| AI       | Analog input         |  |

| AO       | Analog output        |  |

| P        | Power or ground      |  |

| Pin nu | mber  | D.        | D: 4      | D                                                             |                                     |

|--------|-------|-----------|-----------|---------------------------------------------------------------|-------------------------------------|

| LQFP32 | QFN32 | Pin name  | Pin type  | Description                                                   |                                     |

|        |       | PA0       | I/O       | GPIO is configured for input, output, pull-up, pull-down, and |                                     |

|        |       | 1 AU      | 1/0       | other functions through registers.                            |                                     |

|        |       | ANI0      | AI        | ADC channel 0 input                                           |                                     |

|        |       | C0N0      | AI        | ACMP0 negative input 0                                        |                                     |

|        |       | C0OUT0    | О         | ACMP0 output channel 0                                        |                                     |

| 6      | 6     | CTS1      | I         | USART hardware flow input                                     |                                     |

|        |       | MISO      | I/O       | SPI master input/slave output                                 |                                     |

|        |       | SCK00     | I/O       | Serial interface SSPI00 clock I/O                             |                                     |

|        |       | SCL00     | I/O       | Serial interface IIC00 clock I/O                              |                                     |

|        |       |           | TIM1_CH1N | О                                                             | TIM1 channel 1 complementary output |

|        |       | TIM1_CH3  | I/O       | TIM1 channel 3 I/O                                            |                                     |

|        |       | PA1       | I/O       | GPIO is configured for input, output, pull-up, pull-down, and |                                     |

|        |       |           | 1/0       | other functions through registers.                            |                                     |

|        |       | ANI1      | AI        | ADC channel 1 input                                           |                                     |

|        |       | C0P0      | AI        | ACMP0 positive input 0                                        |                                     |

| 7      | 7     | RTS1      | О         | USART hardware flow output                                    |                                     |

|        |       | MOSI      | I/O       | SPI master output/slave input                                 |                                     |

|        |       | SCK       | I/O       | SPI clock input/output                                        |                                     |

|        |       | TIM1_CH2N | О         | TIM1 channel 2 complementary output                           |                                     |

|        |       | TIM1_CH4  | I/O       | TIM1 channel 4 input/output                                   |                                     |

|        |       | PA2       | I/O       | GPIO is configured for input, output, pull-up, pull-down, and |                                     |

|        |       | 1 AZ      | 1/0       | other functions through registers.                            |                                     |

|        |       | ANI2      | AI        | ADC channel 2 input                                           |                                     |

| 8      | 8     | C1N0      | AI        | ACMP1 negative input 0                                        |                                     |

|        |       | C1OUT0    | О         | ACMP1 output channel 0                                        |                                     |

|        |       | TXD1      | О         | USART data output                                             |                                     |

|        |       | MOSI      | I/O       | SPI master output/slave input                                 |                                     |

| Pin nu | mber  | ъ.        | D: .     | 5                                                             |     |                                    |

|--------|-------|-----------|----------|---------------------------------------------------------------|-----|------------------------------------|

| LQFP32 | QFN32 | Pin name  | Pin type | Description                                                   |     |                                    |

|        |       | SCK       | I/O      | SPI clock input/output                                        |     |                                    |

|        |       | SDA       | I/O      | IIC data input/output                                         |     |                                    |

|        |       | TIM3_CH1  | I/O      | TIM3 channel 1 input/output                                   |     |                                    |

|        |       | PA3       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |     |                                    |

|        |       | PAS       | 1/0      | other functions through registers.                            |     |                                    |

|        |       | ANI3      | AI       | ADC channel 3 input                                           |     |                                    |

|        |       | C1P1      | AI       | ACMP1 positive input 1                                        |     |                                    |

|        |       | RXD1      | I        | USART data input                                              |     |                                    |

| 9      | 9     | MOSI      | I/O      | SPI master output/slave input                                 |     |                                    |

|        |       | SDI00     | I        | Serial interface SSPI00 data input                            |     |                                    |

|        |       | SDA00     | I/O      | Serial interface IIC00 data input/output                      |     |                                    |

|        |       | RXD0      | I        | Serial interface UART0 data input                             |     |                                    |

|        |       | SCL       | I/O      | IIC clock input/output                                        |     |                                    |

|        |       | TIM1_CH1  | О        | TIM1 channel 1 input/output                                   |     |                                    |

|        |       | D. 4      | 1/0      | GPIO is configured for input, output, pull-up, pull-down, and |     |                                    |

|        |       |           |          | PA4                                                           | I/O | other functions through registers. |

|        |       |           |          | ANI4                                                          | AI  | ADC channel 4 input                |

|        |       | CK1       | О        | USART synchronous mode clock output                           |     |                                    |

| 10     | 10    | NSS       | I/O      | SPI slave chip select signal input/output                     |     |                                    |

|        |       | SDO00     | О        | Serial interface SSPI00 data output                           |     |                                    |

|        |       | TXD0      | О        | Serial interface UART0 data output                            |     |                                    |

|        |       | TIM3_CH3  | I/O      | TIM3 channel 3 I/O                                            |     |                                    |

|        |       | TIM14_CH1 | I/O      | TIM14 channel 1 input/output                                  |     |                                    |

|        |       | DA5       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |     |                                    |

|        |       | PA5       |          | other functions through registers.                            |     |                                    |

| 11     | 11    | ANI5      | AI       | ADC channel 5 input                                           |     |                                    |

|        |       | SCK       | I/O      | SPI clock input/output                                        |     |                                    |

|        |       | TIM3_CH2  | I/O      | TIM3 channel 2 input/output                                   |     |                                    |

|        |       | DAC       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |     |                                    |

|        |       | PA6       | I/O      | other functions through registers.                            |     |                                    |

|        |       | ANI6      | AI       | ADC channel 6 input                                           |     |                                    |

|        |       | C0OUT1    | О        | ACMP0 output channel 1                                        |     |                                    |

| 12     | 12    | CK1       | О        | USART synchronous mode clock output                           |     |                                    |

|        |       | MISO      | I/O      | SPI master input/slave output                                 |     |                                    |

|        |       | TIM1_BKIN | I        | TIM1 brake signal input                                       |     |                                    |

|        |       | TIM3_CH1  | I/O      | TIM3 channel 1 input/output                                   |     |                                    |

|        |       | TIM16_CH1 | I/O      | TIM16 channel 1 input/output                                  |     |                                    |

|        |       | D 4.7     | 1/0      | GPIO is configured for input, output, pull-up, pull-down, and |     |                                    |

| 12     | 12    | PA7       | I/O      | other functions through registers.                            |     |                                    |

| 13     | 13    | ANI7      | AI       | ADC channel 7 input                                           |     |                                    |

|        |       | C1OUT1    | О        | ACMP1 output channel 1                                        |     |                                    |

| Pin nu | mber  | D.        | D' -     | D 11                                                          |

|--------|-------|-----------|----------|---------------------------------------------------------------|

| LQFP32 | QFN32 | Pin name  | Pin type | Description                                                   |

|        |       | TXD1      | О        | USART data output                                             |

|        |       | MISO      | I/O      | SPI master input/slave output                                 |

|        |       | MOSI      | I/O      | SPI master output/slave input                                 |

|        |       | SDA       | I/O      | IIC data input/output                                         |

|        |       | TIM1_CH1N | О        | TIM1 channel 1 complementary output                           |

|        |       | TIM3_CH2  | I/O      | TIM3 channel 2 input/output                                   |

|        |       | TIM14_CH1 | I/O      | TIM14 channel 1 input/output                                  |

|        |       | TIM17_CH1 | I/O      | TIM17 channel 1 input/output                                  |

|        |       | DAO       | 1/0      | GPIO is configured for input, output, pull-up, pull-down, and |

|        |       | PA8       | I/O      | other functions through registers.                            |

|        |       | ANI24     | AI       | ADC channel 24 input                                          |

|        |       | RXD1      | I        | USART data input                                              |

| 18     | 18    | CK1       | О        | USART synchronous mode clock output                           |

|        |       | MOSI      | I/O      | SPI master output/slave input                                 |

|        |       | SS00      | I        | Serial interface SSPI00 chip select input                     |

|        |       | SCL       | I/O      | IIC clock input/output                                        |

|        |       | TIM1_CH1  | I/O      | TIM1 channel 1 input/output                                   |

|        |       | PA9       | 1/0      | GPIO is configured for input, output, pull-up, pull-down, and |

|        |       |           | I/O      | other functions through registers.                            |

|        |       | ANI25     | AI       | ADC channel 25 input                                          |

|        |       | OSC32_OUT | AO       | XT1 oscillator output                                         |

|        |       | RXD1      | I        | USART data input                                              |

|        |       | TXD1      | 0        | USART data output                                             |

|        |       | SCK       | I/O      | SPI clock input/output                                        |

| 19     | 19    | SDI00     | I        | Serial interface SSPI00 data input                            |

|        |       | SDA00     | I/O      | Serial interface IIC00 data input/output                      |

|        |       | RXD0      | I        | Serial interface UART0 data input                             |

|        |       | SDA       | I/O      | IIC data input/output                                         |

|        |       | SCL       | I/O      | IIC clock input/output                                        |

|        |       | TIM1_BKIN | I        | TIM1 brake input                                              |

|        |       | TIM1_CH2  | I/O      | TIM1 channel 2 input/output                                   |

|        |       |           |          | GPIO is configured for input, output, pull-up, pull-down, and |

|        |       | PA10      | I/O      | other functions through registers.                            |

|        |       | ANI26     | AI       | ADC channel 26 input                                          |

|        |       | OSC32_IN  | AI       | XT1 oscillator input                                          |

|        |       | RXD1      | I        | USART data input                                              |

| 20     | 20    | TXD1      | О        | USART data output                                             |

|        |       | NSS       | I/O      | SPI slave chip select signal input/output                     |

|        |       | SDO00     | 0        | Serial interface SSPI00 data output                           |

|        |       | TXD0      | 0        | Serial interface UART0 data output                            |

|        |       | SDA       | I/O      | IIC data input/output                                         |

| Pin nu | mber  | ъ.         | D: .     | 5                                                                                                |          |   |                                    |

|--------|-------|------------|----------|--------------------------------------------------------------------------------------------------|----------|---|------------------------------------|

| LQFP32 | QFN32 | Pin name   | Pin type | Description                                                                                      |          |   |                                    |

|        |       | SCL        | I/O      | IIC clock input/output                                                                           |          |   |                                    |

|        |       | TIM1_CH3   | I/O      | TIM1 channel 3 I/O                                                                               |          |   |                                    |

|        |       | TIM17_BKIN | I        | TIM17 brake input                                                                                |          |   |                                    |

|        |       | PA11       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and other functions through registers. |          |   |                                    |

|        |       | ANI27      | AI       | ADC channel 27 input                                                                             |          |   |                                    |

|        |       | C0OUT3     | 0        | ACMP0 output channel 3                                                                           |          |   |                                    |

| 21     | 21    | CTS1       | I        | USART hardware flow input                                                                        |          |   |                                    |

|        |       | MISO       | I/O      | SPI master input/slave output                                                                    |          |   |                                    |

|        |       | SCL        | I/O      | IIC clock input/output                                                                           |          |   |                                    |

|        |       | TIM1_CH4   | I/O      | TIM1 channel 4 input/output                                                                      |          |   |                                    |

|        |       | TIMIT_CI14 | 1/0      | GPIO is configured for input, output, pull-up, pull-down, and                                    |          |   |                                    |

|        |       | PA12       | I/O      | other functions through registers.                                                               |          |   |                                    |

|        |       | ANI28      | AI       | ADC channel 28 input                                                                             |          |   |                                    |

|        |       | C1OUT2     | 0        | ACMP1 output channel 2                                                                           |          |   |                                    |

| 22     | 22    | RTS1       | 0        | USART hardware flow output                                                                       |          |   |                                    |

|        |       |            |          | *                                                                                                |          |   |                                    |

|        |       | MOSI       | I/O      | SPI master output/slave input                                                                    |          |   |                                    |

|        |       | SDA        | I/O      | SDA data input/output                                                                            |          |   |                                    |

|        |       |            |          | HIMI_EI                                                                                          | TIM1_ETR | I | TIM1 external trigger signal input |

|        |       | PA13       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and                                    |          |   |                                    |

|        |       | 43,1720    |          | other functions through registers.                                                               |          |   |                                    |

|        |       | ANI29      | AI       | ADC channel 29 input                                                                             |          |   |                                    |

| 23     | 23    | SWDIO      | I/O      | SWD data input/output                                                                            |          |   |                                    |

|        |       | RXD1       | I        | USART data input                                                                                 |          |   |                                    |

|        |       | MISO       | I/O      | SPI master input/slave output                                                                    |          |   |                                    |

|        |       | TIM1_CH2   | I/O      | TIM1 channel 2 input/output                                                                      |          |   |                                    |

|        |       | PA14       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and                                    |          |   |                                    |

|        |       |            |          | other functions through registers.                                                               |          |   |                                    |

| 24     | 24    | ANI30      | AI       | ADC channel 30 input                                                                             |          |   |                                    |

|        |       | SWCLK      | I        | SWD clock input                                                                                  |          |   |                                    |

|        |       | TXD1       | О        | USART data output                                                                                |          |   |                                    |

|        |       | PA15       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and                                    |          |   |                                    |

|        |       |            |          | other functions through registers.                                                               |          |   |                                    |

| 25 25  | 25    | ANI31      | AI       | ADC channel 31 input                                                                             |          |   |                                    |

|        |       | RXD1       | I        | USART data input                                                                                 |          |   |                                    |

|        |       | NSS        | I/O      | SPI slave chip select signal input/output                                                        |          |   |                                    |

|        |       | PB0        | I/O      | GPIO is configured for input, output, pull-up, pull-down, and                                    |          |   |                                    |

|        |       | 100        | 1/0      | other functions through registers.                                                               |          |   |                                    |

| 14     | 14    | ANI8       | AI       | ADC channel 8 input                                                                              |          |   |                                    |

|        |       | C0OUT2     | О        | ACMP0 output channel 2                                                                           |          |   |                                    |

|        |       | NSS        | I/O      | SPI slave chip select signal input/output                                                        |          |   |                                    |

| Pin nu | mber  | D:         | D:       | Description                                                   |  |  |  |     |                                                               |

|--------|-------|------------|----------|---------------------------------------------------------------|--|--|--|-----|---------------------------------------------------------------|

| LQFP32 | QFN32 | Pin name   | Pin type | Description                                                   |  |  |  |     |                                                               |

|        |       | TIM1_CH2N  | О        | TIM1channel 2 complementary output                            |  |  |  |     |                                                               |

|        |       | TIM3_CH3   | I/O      | TIM3 channel 3 I/O                                            |  |  |  |     |                                                               |

|        |       | PB1        | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |  |  |  |     |                                                               |

|        |       | FBI        | 1/0      | other functions through registers.                            |  |  |  |     |                                                               |

|        |       | ANI9       | AI       | ADC channel 9 input                                           |  |  |  |     |                                                               |

| 15     | 15    | C0N1       | AI       | ACMP0 negative input 1                                        |  |  |  |     |                                                               |

|        |       | TIM1_CH3N  | O        | TIM1 channel 3 complementary output                           |  |  |  |     |                                                               |

|        |       | TIM3_CH4   | I/O      | TIM3 channel 4 input/output                                   |  |  |  |     |                                                               |

|        |       | TIM14_CH1  | I/O      | TIM14 channel 1 input/output                                  |  |  |  |     |                                                               |

|        |       | DDO        | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |  |  |  |     |                                                               |

|        |       | PB2        | I/O      | other functions through registers.                            |  |  |  |     |                                                               |

|        |       | ANI10      | AI       | ADC channel 10 input                                          |  |  |  |     |                                                               |

| -      | 17    | C0P1       | AI       | ACMP0 positive input 1                                        |  |  |  |     |                                                               |

|        |       | RXD1       | I        | USART data input                                              |  |  |  |     |                                                               |

|        |       | SCK00      | I/O      | Serial interface SSPI00 clock I/O                             |  |  |  |     |                                                               |

|        |       | SCL00      | I/O      | Serial interface IIC00 clock I/O                              |  |  |  |     |                                                               |

|        |       |            |          |                                                               |  |  |  | 7/0 | GPIO is configured for input, output, pull-up, pull-down, and |

|        |       | PB3        | I/O      | other functions through registers.                            |  |  |  |     |                                                               |

|        | 26 26 | ANI11      | AI       | ADC channel 11 input                                          |  |  |  |     |                                                               |

| 26     |       | C1N1       | AI       | ACMP1 negative input 1                                        |  |  |  |     |                                                               |

|        |       | RTS1       | О        | USART hardware flow output                                    |  |  |  |     |                                                               |

|        |       | SCK        | I/O      | SPI clock input/output                                        |  |  |  |     |                                                               |

|        |       | TIM1_CH2   | I/O      | TIM1 channel 2 input/output                                   |  |  |  |     |                                                               |

|        |       | DD 4       | 4 I/O    | GPIO is configured for input, output, pull-up, pull-down, and |  |  |  |     |                                                               |

|        |       | PB4        |          | other functions through registers.                            |  |  |  |     |                                                               |

|        |       | ANI12      | AI       | ADC channel 12 input                                          |  |  |  |     |                                                               |

|        |       | C1P2       | AI       | ACMP1 positive input 2                                        |  |  |  |     |                                                               |

| 27     | 27    | CTS1       | I        | USART hardware flow input                                     |  |  |  |     |                                                               |

|        |       | MISO       | I/O      | SPI master input/slave output                                 |  |  |  |     |                                                               |

|        |       | TIM3_CH1   | I/O      | TIM3 channel 1 input/output                                   |  |  |  |     |                                                               |

|        |       | TIM17_BKIN | I        | TIM17 external brake signal input                             |  |  |  |     |                                                               |

|        |       | DD 5       | 1/0      | GPIO is configured for input, output, pull-up, pull-down, and |  |  |  |     |                                                               |

|        |       | PB5        | I/O      | other functions through registers.                            |  |  |  |     |                                                               |

|        |       | ANI13      | AI       | ADC channel 13 input                                          |  |  |  |     |                                                               |

|        |       | C0OUT4     | О        | ACMP0 output channel 4                                        |  |  |  |     |                                                               |

| 28     | 28    | CK1        | О        | USART synchronous mode clock output                           |  |  |  |     |                                                               |

|        |       | MOSI       | I/O      | SP1 master output/slave input                                 |  |  |  |     |                                                               |

|        |       | SMBA       | I/O      | IIC SMBus mode alarm signal input/output                      |  |  |  |     |                                                               |

|        |       | TIM3_CH2   | I/O      | TIM3 channel 2 input/output                                   |  |  |  |     |                                                               |

|        |       | TIM16_BKIN | I        | TIM16 external brake signal input                             |  |  |  |     |                                                               |

| 29     | 29    | PB6        | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |  |  |  |     |                                                               |

|        | ·     |            | ·        | •                                                             |  |  |  |     |                                                               |

| Pin nu | mber  | D.            | D: 4     | B                                                                                                |

|--------|-------|---------------|----------|--------------------------------------------------------------------------------------------------|

| LQFP32 | QFN32 | Pin name      | Pin type | Description                                                                                      |

|        |       |               |          | other functions through registers.                                                               |

|        |       | ANI14         | AI       | ADC channel 14 input                                                                             |

|        |       | C1P3          | AI       | ACMP1 positive input 3                                                                           |

|        |       | TXD1          | О        | USART data output                                                                                |

|        |       | SDI00         | I        | Serial interface SSPI00 data input                                                               |

|        |       | SDA00         | I/O      | Serial interface IIC00 data input/output                                                         |

|        |       | RXD0          | I        | Serial interface UART0 data input                                                                |

|        |       | SCL           | I/O      | IIC clock input/output                                                                           |

|        |       | TIM1_CH3      | I/O      | TIM1 channel 3 I/O                                                                               |

|        |       | TIM16_CH1N    | О        | TIM16 channel 1 complementary output                                                             |

|        |       | PB7           | I/O      | GPIO is configured for input, output, pull-up, pull-down, and other functions through registers. |

|        |       | ANI15         | AI       | ADC channel 15 input                                                                             |

|        |       | C1N2          | AI       | ACMP1 negative input 2                                                                           |

| 30     | 30    | RXD1          | I        | USART data input                                                                                 |

|        |       | SDO00         | О        | Serial interface SSPI00 data output                                                              |

|        |       | TXD0          | О        | Serial interface UART0 data output                                                               |

|        |       | SDA           | I/O      | IIC data input/output                                                                            |

|        |       | TIM17_CH1N    | О        | TIM17 channel 1 complementary output                                                             |

|        |       | PB8           |          | GPIO is configured for input, output, pull-up, pull-down, and                                    |

|        |       |               | I/O      | other functions through registers.                                                               |

|        |       | ANI32         | AI       | ADC channel 32 input                                                                             |

|        |       | C0P2          | AI       | ACMP0 positive input 2                                                                           |

|        |       | TXD1          | О        | USART data output                                                                                |

|        | 32    | SCK00         | I/O      | Serial interface SSPI00 clock I/O                                                                |

|        |       | SCL00         | I/O      | Serial interface IIC00 clock I/O                                                                 |

|        |       | SS00          | I        | Serial interface SSPI00 chip select input                                                        |

|        |       | SDA           | I/O      | IIC data input/output                                                                            |

|        |       | TIM16_CH1     | I/O      | TIM16 channel 1 input/output                                                                     |

|        |       | TIM17_CH1     | I/O      | TIM17 channel 1 input/output                                                                     |

|        |       | PF0           | I/O      | GPIO is configured for input, output, pull-up, pull-down, and other functions through registers. |

|        |       | ANI16         | AI       | ADC channel 16 input                                                                             |

|        |       | RXD1          | I        | USART data input                                                                                 |

| 2      | 2     | SCK00         | I/O      | Serial interface SSPI00 clock I/O                                                                |

|        |       | SCL00         | I/O      | Serial interface IIC00 clock I/O                                                                 |

|        |       | SDA           | I/O      | IIC data input/output                                                                            |

|        |       | TIM14_CH1     | I/O      | TIM14 channel 1 input/output                                                                     |

|        |       | 111111-7_0111 | 1,0      | GPIO is configured for input, output, pull-up, pull-down, and                                    |

| 3      | 3     | PF1           | I/O      | other functions through registers.                                                               |

| ]      |       | ANI17         | AI       | ADC channel 17 input                                                                             |

|        |       | 111111/       | 731      | 7 De chamier 17 input                                                                            |

| Pin nu | ımber | D:        | D:       | Description                                                   |

|--------|-------|-----------|----------|---------------------------------------------------------------|

| LQFP32 | QFN32 | Pin name  | Pin type | Description                                                   |

|        |       | TXD1      | 0        | USART data output                                             |

|        |       | NSS       | I/O      | SPI slave chip select signal input/output                     |

|        |       | SDI00     | I        | Serial interface SSPI00 data input                            |

|        |       | SDA00     | I/O      | Serial interface IIC00 data input/output                      |

|        |       | RXD0      | I        | Serial interface UART0 data input                             |

|        |       | SCL       | I/O      | IIC clock input/output                                        |

|        |       | TIM14_CH1 | I/O      | TIM14 channel 1 input/output                                  |

|        |       | PF2       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |

|        |       | FF2       | 1/0      | other functions through registers.                            |

| 4      | 4     | ANI18     | AI       | ADC channel 18 input                                          |

| 4      | 4 4   | SDO00     | О        | Serial interface SSPI00 data output                           |

|        |       | TXD0      | О        | Serial interface UART0 data output                            |

|        |       | NRST      | I        | External reset pin                                            |

|        |       | PF3       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |

|        |       | FF3       | 1/0      | other functions through registers.                            |

|        |       | ANI19     | AI       | ADC channel 19 input                                          |

|        |       | C1P0      | AI       | ACMP1 positive input 0                                        |

| 5      | 5     | TXD1      | О        | USART data output                                             |

| 3      | 3     | NSS       | I/O      | SPI slave chip select signal input/output                     |

|        |       | SDI00     | I        | Serial interface SSPI00 data input                            |

|        |       | SDA00     | I/O      | Serial interface IIC00 data input/output                      |

|        |       | RXD0      | I        | Serial interface UART0 data input                             |

|        |       | TIM3_CH3  | I/O      | TIM3 channel 3 I/O                                            |

|        |       | PF4       | I/O      | GPIO is configured for input, output, pull-up, pull-down, and |

| 31     | 31    |           | 1/0      | other functions through registers.                            |

|        |       | ANI20     | AI       | ADC channel 20 input                                          |

| 16     | 16    | VSS       | P        | Ground pin                                                    |

| 1      | 1     | VDD       | P        | Supply voltage input pin                                      |

| 32     | -     | VSS       | P        | Ground pin                                                    |

| 17     | -     | VDD       | P        | Supply voltage input pin                                      |

# **5 Function Summary**

## 5.1 ARM® Cortex®-M0+ Core

The ARM Cortex-M0+ processor is a next-generation product in the ARM processor family, designed specifically for embedded systems. It provides a low-cost platform aimed at meeting the demands of microcontrollers with fewer pins and low power consumption, while offering excellent computational performance and advanced system response to interrupts.

The Cortex-M0+ processor is a 32-bit microcontroller that delivers outstanding code efficiency and high-performance expectations of the ARM core, differentiating it from 8-bit and 16-bit devices with the same memory size. The Cortex-M0+ processor features 32 address lines, supporting memory space up to 4GB.

The CMS32C030 series uses the embedded ARM core, ensuring compatibility with all ARM tools and software.

## 5.2 Memory

## 5.2.1 Flash Memory

This product features built-in flash memory that supports programming, erasing, and rewriting with the following functionalities:

- Program and data share 64K of memory space.

- 1KB dedicated data flash memory.

- Supports page erase, with each page size being 512 bytes.

- Supports byte/half-word/word programming.

### 5.2.2 SRAM

The chip has an embedded SRAM of 8K bytes.

## 5.3 Clock Generation and Start-Up

A clock generation circuit is a circuit that generates a clock to the CPU and peripheral hardware. There are two types of system clocks and clock oscillation circuits.

## 5.3.1 Main System Clock

• High-speed on-chip oscillator (High-speed OCO): The frequency can be selected via the option byte for oscillation. After the reset is released, the CPU starts running with this high-speed on-chip oscillator clock by default. The oscillator can be stopped by executing the deep sleep instruction or by setting the HIOSTOP bit. The frequency set by the option byte can be changed using the frequency selection register of the high-speed on-chip oscillator. The maximum frequency is 48 MHz.

## 5.3.2 Subsystem Clock

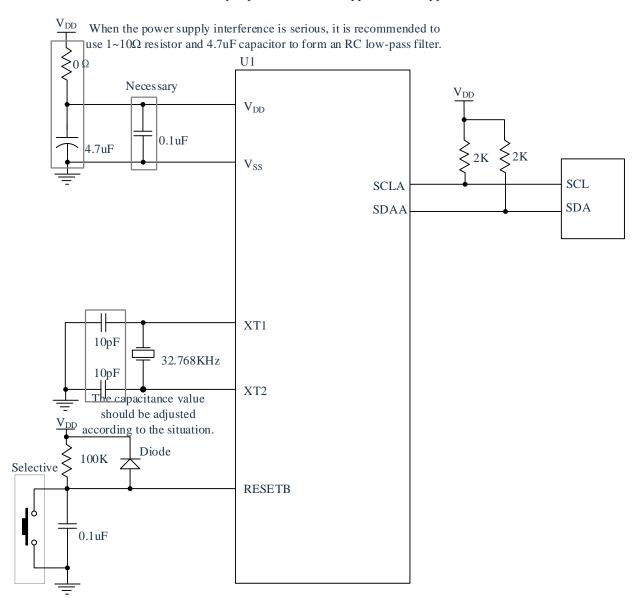

- XT1 Oscillator Circuit: By connecting a 32.768 kHz resonator to the pins (XT1 and XT2), a 32.768 kHz clock oscillation can be generated. The oscillation can be stopped by setting the XTSTOP bit.

- Low-speed on-chip oscillator (Low-speed OCO): Generates a clock oscillation at 32 kHz (typical). The low-speed on-chip oscillator clock can be used as the CPU clock. The following peripheral hardware can run using the low-speed on-chip oscillator clock:

- -Independent Watch Dog Timer (IWDG)

- -15-bit interval timer

## 5.4 Power Management

## **5.4.1** Power Supply Method

VDD: External power supply, and voltage range is 2.0 to 5.5V.

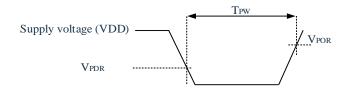

#### 5.4.2 Power-On Reset

The power-on-reset circuit (POR) has the following functions:

- An internal reset signal is generated when power is applied. If the supply voltage (VDD) is greater than the detection voltage (V<sub>POR</sub>), the reset is released. However, the reset state must be maintained by a voltage detection circuit or an external reset until the operating voltage range is reached.

- The power supply voltage (VDD) is compared with the detection voltage (V<sub>POR</sub>) and an internal reset signal is generated when VDD < V<sub>POR</sub>. However, when the power supply drops, it must be shifted to deep sleep mode or set to reset by voltage detection circuit or external reset before it is less than the operating voltage range. To restart operation, it must be confirmed that the power supply voltage has returned to the operating voltage range.

## **5.4.3** Voltage Detection

The voltage detection circuit sets the operation mode and detection voltage ( $V_{LVDH}$ ,  $V_{LVDL}$ ,  $V_{LVD}$ ) by means of option bytes. The voltage detection (LVD) circuit has the following functions:

- The internal reset or interrupt request signal is generated by comparing the power supply voltage (V<sub>DD</sub>) with the detection voltage (V<sub>LVDH</sub>, V<sub>LVDL</sub>, V<sub>LVD</sub>).

- The detection voltage of the supply voltage  $(V_{LVDH}, V_{LVDL}, V_{LVD})$  can be selected via the option byte.

- Able to run in deep sleep mode.

- When the power supply rises, the reset state must be maintained by voltage detection circuitry or external reset before the operating voltage range is reached. When the power supply drops, it must be shifted to deep sleep mode or set to reset state by voltage detection circuit or external reset before it is less than the operating voltage range.

- The operating voltage range varies according to the setting of the user option byte.

- The LVD output can be used as a TIM1/TIM16/TIM17 brake input.

## **5.5** Low-Power Consumption Modes

The product supports two low-power modes to achieve the best trade-off between low power consumption, short startup time, and available wake-up sources:

- Sleep Mode: Entered by executing the sleep instruction. Sleep mode stops the CPU's operating clock while maintaining oscillation of other clocks, such as the high-speed system clock oscillator, high-speed on-chip oscillator, or external low-speed clock oscillator. While this mode doesn't reduce working current as much as deep sleep mode, it is an effective mode when you need to quickly resume processing via interrupt requests or for intermittent operation.

- Deep Sleep Mode: Entered by executing the deep sleep instruction. Deep sleep mode stops the

oscillation of both the high-speed system clock oscillator and high-speed on-chip oscillator,

effectively halting the entire system. This significantly reduces the chip's operating current. Deep

sleep mode can also be interrupted for intermittent operation, but requires a stable waiting period for

oscillator stabilization after waking up. If immediate processing is necessary via an interrupt request,

sleep mode must be chosen instead.

In both modes, registers, flags, and data memory are preserved with their content set before entering the standby mode. The output latches and output buffers of the input/output ports also retain their state.

## **5.6** Reset Function

The following eight methods can generate a reset signal:

- (1) External reset input through the RESETB pin.

- (2) Internal reset generated by the program failure detection of the Windowed Watch Dog Timer (WWDG).

- (3) Internal reset generated by the program failure detection of the Independent Watch Dog Timer (IWDG).

- (4) Internal reset generated by the Power-On Reset (POR) circuit comparing the power supply voltage with the detection voltage.

- (5) Internal reset generated by the Low Voltage Detection (LVD) circuit comparing the power supply voltage with the detection voltage.

- (6) Internal reset generated when the System Reset Request register bit (AIRCR.SYSRESETREQ) is set to 1.

- (7) Internal reset generated by accessing an invalid memory.

- (8) TRIM positive and negative code reset.

Both internal and external resets are the same; after the reset signal is generated, the program execution begins from the user-defined program starting address.

# 5.7 Interrupt Function

The Cortex-M0+ processor includes a Nested Vectored Interrupt Controller (NVIC), which supports up to 32 interrupt request (IRQ) inputs and 1 Non-Maskable Interrupt (NMI) input. Additionally, the processor supports multiple internal exceptions.

This product handles 23 maskable interrupt requests (IRQ), as detailed in the corresponding chapter of the user manual. The actual number of interrupt sources may vary depending on the product.

## 5.8 Timers

## **5.8.1** Advanced Control Timer (TIM1)

The advanced control timer TIM1 contains a 16-bit auto-reload counter, driven by a programmable prescaler. This type of timer can be used for various purposes, including measuring the pulse width of input signals (input capture) or generating output waveforms (output compare, PWM, and complementary PWM with dead time insertion).

The advanced timer (TIM1) and general-purpose (TIMx) timers are fully independent and do not share any resources. They can be synchronized.

TIM1 timer has 4 independent channels, which can be used for:

- Input capture

- Output compare

- PWM generation (edge and center-aligned modes)

- Single pulse mode output

TIM1 can reset its output signal to a known state when a brake input is received.

When controlled by external signals, TIM1 can achieve synchronization of multiple interconnected timers.

TIM1 supports incremental (quadrature) encoder and Hall sensor circuits.

TIM1 supports external clock trigger inputs or cycle-by-cycle current management.

TIM1 timer supports DMA functionality.

In MCU debug mode, TIM1 can be set to stop.

#### **5.8.2** General-Purpose Timer (TIM3)

The TIM3 general-purpose timer is a 16-bit auto-reload counter driven by a 16-bit programmable pre-scaler. It has 4 independent channels that can be used for input capture/output compare, PWM, or single pulse mode output.

When controlled by external signals, TIM3 can achieve synchronization of multiple interconnected timers.

TIM3 timer supports DMA functionality.

TIM3 supports incremental (quadrature) encoder and Hall sensor circuits.

TIM3 supports external clock trigger inputs or cycle-by-cycle current management.

In MCU debug mode, TIM3 can be set to stop.

#### **5.8.3** General-Purpose Timer (TIM14)

The TIM14 general-purpose timer is a 16-bit auto-reload counter driven by a 16-bit programmable prescaler.

TIM14 has 1 independent channel, which can be used for input capture/output compare, PWM, or single pulse mode output.

In MCU debug mode, TIM14 can be set to stop.

## **5.8.4** General-Purpose Timer (TIM16/TIM17)

The general timers TIM16/TIM17 are 16-bit auto-reload counters driven by a 16-bit programmable prescaler.

TIM16/TIM17 has 1 independent channel, which can be used for input capture/output compare, PWM, or single pulse mode output.

TIM16/TIM17 has complementary outputs with programmable dead-time.

TIM16/TIM17 can reset its output signal to a known state when a brake input is received.

TIM16/TIM17 timers support DMA functionality.

In MCU debug mode, TIM16/17 can be set to stop.

#### 5.8.5 15-Bit Interval Timer

This product has a built-in 15-bit interval timer, which can generate interrupts (INTIT) at a preset time interval, and can be used to wake up from deep sleep mode. The counting clock can be selected from either the external low-speed clock or the on-chip low-speed clock.

## **5.8.6** Windowed Watch Dog Timer (WWDG)

The windowed watch dog is based on a 7-bit down-counter. When an issue occurs, it can reset the system as a watch dog. The counting clock is the APB prescaled clock. It can generate an early wake-up interrupt. In MCU debug mode, the windowed watch dog can be set to stop.

## **5.8.7** Independent Watch Dog Timer (IWDG)

The IWDG is best suited for applications that require a watch dog to operate completely independently of the main program and where timing precision is less critical. The IWDG is clocked by a low-speed on-chip oscillator (LSI), so it continues to function even if the main clock fails.

- When the system generates a LOOKUP, the IWDG counter is enabled by force, and after the LOOKUP is revoked, the IWDG counter is disabled.

- The IWDG hardware mode can be enabled through option bytes.

- The IWDG is a wake-up source for deep sleep mode, waking up the system with a reset.

- In MCU debug mode, the independent watch dog can be set to stop.

## 5.8.8 SysTick Timer

This timer is designed specifically for real-time operating systems, but it can also be used as a standard decrementing counter. Its features include:

- 24-bit down-counter

- Auto-reload capability

- Generates an interrupt (which can be masked) when the counter reaches 0.

## 5.9 Communication Module

#### 5.9.1 Universal Serial Communication Unit

This product includes 1 Universal Serial Communication Unit with 2 serial channels, capable of supporting 3-wire serial (SSPI), UART, and simplified I<sup>2</sup>C communication functions. The functionality of each channel is assigned as follows.

#### (1) 3-Wire Serial Interface (Simplified SPI)

Data transmission and reception are synchronized with the serial clock (SCLK) output by the master device.

This is a clock-synchronous communication interface using 3 communication lines: 1 serial clock (SCLK), 1 serial data output (SDO), and 1 serial data input (SDI).

## [Data Transmission and Reception]

- 7-bit or 8-bit data length

- Control of the phase for transmitting and receiving data

- MSB/LSB priority selection

- Setting of data level for transmitting and receiving data

## [Clock Control]

- Selection of master or slave mode

- Control of the phase for input/output clock

- Transfer cycle generated by the prescaler and internal counter of the channel

- Maximum transfer rate

Master communication: Max. 6MHz Slave communication: Max. 6MHz

#### [Interrupt Functions]

- Transfer end interrupt, buffer empty interrupt

#### [Error Detection Flags]

Overflow error

## (2) Simplified SPI with Slave Chip Select Function

Supports SPI serial communication interface with a slave chip select input function. This is a clock-synchronous communication interface using 4 communication lines: 1 slave chip select input (SS), 1 serial clock (SCLK), 1 serial data output (SDO), and 1 serial data input (SDI).

## [Data Transmission and Reception]

- 7-bit or 8-bit data length

- Control of the phase for transmitting and receiving data

- MSB/LSB priority selection

- Setting of data level for transmitting and receiving data

### [Clock Control]

- Control of the phase for input/output clock

- Transfer cycles generated by the prescaler and internal counter of the channel

- Maximum transfer rate

Slave communication: Max.6MHz

## [Interrupt Functions]

- Transfer end interrupt, buffer empty interrupt

#### [Error Detection Flags]

Overflow error

#### (3) UART

The function of asynchronous communication via 2 lines, Serial Data Transmission (TxD) and Serial Data Reception (RxD). These 2 communication lines transmit and receive data in frames, consisting of a start bit, data, parity bit, and stop bit, using an internal baud rate for asynchronous communication with other devices. Full-duplex UART communication is supported by using two dedicated channels: one for transmission (even channel) and one for reception (odd channel).

#### [Data Transmission and Reception]

- 7-bit or 8-bit data length

- MSB/LSB priority selection

- Data level setting for transmission and reception, with inversion option

- Parity bit addition and parity function

- Stop bit addition

#### [Interrupt Functions]

- Transfer end interrupt, buffer empty interrupt

- Error interrupt triggered by frame error, parity error, or overflow error

## [Error Detection Flags]

- Frame error, parity error, overflow error

## (4) Simplified I<sup>2</sup>C

This function provides clock-synchronized communication with multiple devices via two lines: Serial Clock (SCL) and Serial Data (SDA). Since this simplified I<sup>2</sup>C is designed for single-device communication, such as with flash memory or A/D converters, it can only function as the master device. Start and stop conditions must comply with AC characteristics and are handled by software.

#### [Data Transmission and Reception]

- Master transmission, master reception (only for single-master functionality)

- ACK output and ACK detection features

- 8-bit data length (for address transmission, the high 7 bits specify the address, and the least significant bit is used for R/W control)

- Start and stop conditions generated by software

#### [Interrupt Functions]

- Transfer end interrupt

## [Error Detection Flags]

- ACK error, overflow error

## [Unsupported Features in Simplified I<sup>2</sup>C]

- Slave transmission, slave reception

- Arbitration failure detection

- Wait detection function

#### **5.9.2** Serial Interface IIC

The I<sup>2</sup>C (Inter-Integrated Circuit) bus interface is used as an interface between the microcontroller and the I<sup>2</sup>C serial bus. It provides multi-master mode functionality and can control all I<sup>2</sup>C bus-specific sequences, protocols, arbitration, and timing. It supports both standard and fast modes and is also compatible with SMBus 2.0. It can be used for various purposes, including CRC generation and verification, SMBus (System Management Bus), and PMBus (Power Management Bus). Depending on the device, DMA functionality can be utilized to reduce the workload of the CPU. Its features are as follows:

- Parallel bus/I<sup>2</sup>C protocol converter

- Multi-master mode functionality: The same interface can be used as both master and slave mode

- I<sup>2</sup>C master mode features:

- Clock generation

- Start and stop bit generation

- I<sup>2</sup>C slave mode features:

- Programmable I<sup>2</sup>C address detection

- Dual address mode, allowing responses to two slave addresses

- Stop bit detection

- 7-bit/10-bit addressing and broadcast call generation and detection

- Supports different communication speeds:

- Standard speed (up to 100 KHz)

- Fast speed (up to 400 KHz)

- Status flags:

- Transmit/Receive mode flag

- Byte transfer end flag

- I<sup>2</sup>C busy flag

- Error flags:

- Arbitration lost in master mode

- Acknowledgement failure after address/data transfer

- Detection of erroneous start and stop bits

- Overflow/underflow after clock stretching is disabled

- Two interrupt vectors:

- One interrupt triggered by successful address/data byte transfer

- One interrupt triggered by error status

- Optional clock stretching

- 1-byte buffer with DMA functionality

- Configurable PEC (Packet Error Check) generation or verification:

- In Tx mode, the PEC value can be transmitted as the last byte

- PEC error check for the last received byte

- SMBus 2.0 compatibility:

- 25 ms clock low timeout delay

- 10 ms cumulative clock low extension for master device

- 25 ms cumulative clock low extension for slave device

- Hardware PEC generation/verification with ACK control

- Supports Address Resolution Protocol (ARP)

- PMBus compatibility

#### **5.9.3 SPI Communication Unit**

The Serial Peripheral Interface (SPI) provides half-duplex/full-duplex synchronous serial communication with external devices. The interface can be configured as the master mode, in which case it provides the communication clock (SCK) for the external slave devices. The interface can also operate in a multi-master mode.

It can be used for various purposes, including half-duplex synchronous transfer based on two wires, where one wire can act as a bidirectional data line, or using CRC checks for reliable communication. Its features are as follows:

- Full-duplex synchronous transfer based on three lines

- Half-duplex synchronous transfer based on two wires, where one can act as a bidirectional data line

- 8-bit or 16-bit transfer frame format selection

- Master mode or slave mode operation

- Multi-master mode functionality

- 8 master mode baud rate prescalers (maximum value is f<sub>PCLK</sub>/2)

- Slave mode frequency (maximum value is 6 MHz)

- Faster communication for both master and slave modes

- Hardware or software management of NSS for both master and slave modes: Dynamic switching between master/slave operation

- Programmable clock polarity and phase

- Programmable data order, shift MSB or LSB first

- Dedicated transmit and receive flags that can trigger interrupts

- SPI bus busy status flag

- SPI TI mode

- Hardware CRC functionality for ensuring reliable communication:

- In transmit mode, the CRC value can be sent as the last byte

- CRC error checking is automatically performed based on the last received byte

- Master mode fault, overflow, and CRC error flags that can trigger interrupts

- 1-byte transmit and receive buffers with DMA functionality: Transmission and reception requests

## 5.9.4 Serial Synchronous/Asynchronous Communication Unit (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) is capable of flexible full-duplex data exchange with external devices, meeting the requirements of industrial standard NRZ asynchronous serial data format for external devices. The USART provides multiple band rates through a fractional band rate generator.

It supports synchronous unidirectional communication and half-duplex single-wire communication; it also supports LIN (Local Interconnect Network), IrDA (Infrared Data Association) SIR ENDEC standards, and modem operation (CTS/RTS). Additionally, it supports multiprocessor communication.

High-speed data communication can be achieved by configuring multiple buffers and using DMA. Its features are as follows:

- Full-duplex asynchronous communication

- NRZ standard format (mark/space)

- Fractional baud rate generator system

- Universal programmable baud rate for the transceiver

- Programmable data word length (8 bits or 9 bits)